Sådan oprettes en simpel seriel UART-sender i verilog HDL

De fleste Universal Asynchronous Receiver Transmitter (UART), som jeg fandt online, er for komplicerede og vanskelige at forstå, her vil jeg forklare nogle enkle teorier og også kode om, hvordan man bygger en.

Lad os først tale om, hvordan sendere fungerer. Det grundlæggende princip er at sende flere bits data over en enkelt linje. I vores sender er disse data parallelle, men for at reducere antallet af ledninger, der kræves, bruger vi seriel kommunikation, der konverteres til parallel i den modtagende ende.

De grundlæggende ting, vi har brug for, er følgende:

- En urdeler (vores tæller)

Dette gør det muligt for os at sende data med en bestemt hastighed (baudrate). Vores modtager prøver og tager dataene bit for bit.

- Et skiftregister

Vi har brug for at vide, hvor mange bits ad gangen vi sender, vores skiftregister vil have en startbit, databits, paritetsbit (valgfri), slutbit.

- Et tilstandsdiagram

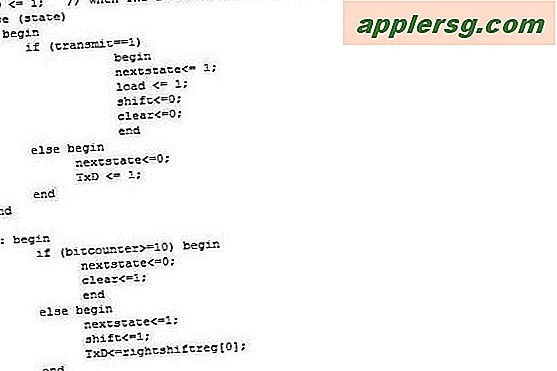

Før vi skriver en kode, skal vi tænke på, hvad vi skal skabe, og den bedste måde er at oprette et tilstandsdiagram over vores design. Vi ved, at vi for en sender har brug for to tilstande, tomgang og transmission.

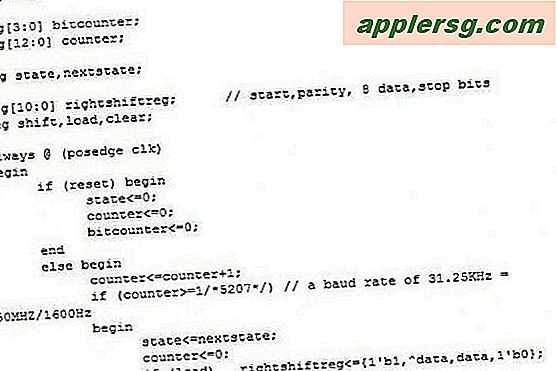

Efter at have et tilstandsdiagram kan vi nu beregne, hvad vores tæller vil være. Dette gøres ved at bruge:

tæller = FPGA-urhastighed / baudrate

I dette eksempel bruger jeg en baudrate på 9600, hvilket gør min tæller = 5208.

Til sidst beregner vi vores skiftregister og færdig med at skrive vores statsmaskine. I min prøvekode bruger jeg en startbit, paritetsbit, 8 bit data og slutbit. Dette er i alt 11 bits.

Begge billeder i trin 2 og 3 sammen i det samme modul udfylder vores senderkode, der kræves for at programmere til FPGA. Denne kode fungerer sammen med en anden FPGA tilsluttet serielt eller med windows hyperterminal blandt anden hardware. Kan let ændres til at arbejde med meget mere.

Til sidst opretter vi en testarmatur til at rette eventuelle fejl og simulere vores program inden programmering af FPGA.

Dette afslutter senderen. Skriv kommentarer, hvis du har spørgsmål eller føler, at der mangler noget her.

Tips

Både sender og modtager skal kende den baudhastighed, hvormed data sendes.

![iOS 10.3.3 Update Udgivet til iPhone, iPad [IPSW Download Links]](http://applersg.com/img/ipad/376/ios-10-3-3-update-released.jpg)